삼성전자가 세계 최초로 차세대 게이트올어라운드(GAA·Gate-All-Around)) 기반 3나노미터(㎚=10억분의 1m) 공정 양산 초읽기에 들어갔다. GAA 신공정은 글로벌 파운드리(반도체 위탁생산) 1위 대만 TSMC를 단숨에 따라잡을 삼성전자의 승부수로 평가받는다. TSMC보다 6개월가량 3나노 공정 양산을 먼저 시작해 퀄컴, 엔비디아 등 핵심 고객을 선점하고 파운드리 재진출을 선언한 인텔 추격까지 따돌리겠다는 복안이다.

일각에선 삼성전자가 기술적 한계를 극복하지 못하고 양산 시기를 미룰 것이라는 소문도 돌았지만 회사 관계자는 이를 일축했다. 한 업계 관계자는 "3나노 GAA 반도체 개발이 기존 계획대로 차질없이 진행된 것으로 알고 있다"며 "상반기 내에 3나노를 양산하겠다는 경영진 의지가 워낙 강하기 때문에 이번 주 내에 소식이 들릴 것"이라고 말했다.

이번 양산을 통해 삼성전자는 세계 반도체 기업들의 초미세 공정 경쟁에서 한 발 앞서 나갈 것으로 보인다. 3나노는 반도체 회로 선폭을 머리카락 굵기의 10만분의 3으로 좁힌 셈이기 때문이다. 반도체는 회로 간격이 미세할수록 성능이 높아지고 전력소비가 줄어든다. 웨이퍼(반도체 원판)에서 나오는 반도체 숫자가 증가해 생산 효율성도 개선된다. 반도체 업계가 나노 기술 경쟁을 벌이는 이유다.

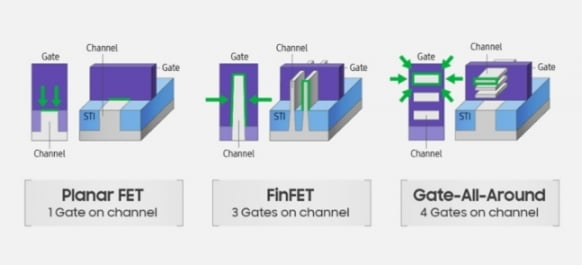

삼성전자는 여기에 GAA 신공정을 더했다. 반도체 내 전류 흐름을 위해 스위치를 켜고 끄는 트랜지스터 제조 기술을 아예 바꾼 것이다. 현재 반도체 공정에는 상어 지느러미를 닮았다고 해서 이름 붙은 '핀펫(FinFET) 기술'이 쓰이는데 반도체 크기가 계속 작아지면서 전류 제어 한계에 봉착했다. 전류 제어 역할을 하는 게이트가 제 역할을 하지 못해 누설 전류가 생기면서 전력 효율이 떨어지는 탓이다.

반면 GAA 구조에서는 전류의 흐름을 보다 세밀하게 조정할 수 있는 만큼 전력 효율이 보다 개선될 수 있다. 핀펫은 전류가 흐르는 채널이 3개면이었지만 GAA는 모든 면에서 전류가 흐르는 구조여서 트랜지스터 사이즈가 작아진다. 따라서 궁극적으로 반도체를 더 소형화할 수 있게 된다. 3나노 GAA 공정을 활용하면 7나노 핀펫 대비 칩 면적은 45%, 소비전력의 경우 50% 절감할 수 있다는 설명이다. 성능 역시 약 35% 향상될 것으로 예상된다. 이 기술은 핀펫 공정과 호환성이 높아 기존 설비·기술을 그대로 쓸 수 있다는 장점도 있다.

업계는 삼성전자가 파운드리 기술력을 예상보다 빠르게 끌어올린 것으로 본다. 2030년까지 시스템 반도체 분야 1위 달성을 목표로 한 삼성전자의 '시스템 반도체 2030 비전'도 3나노 공개를 기점으로 본 궤도에 오를 것으로 관측했다.

TSMC 역시 올 하반기 3나노 반도체를 양산할 계획을 밝힌 바 있다. 하지만 삼성전자가 계획대로 3나노 양산 발표를 진행할 경우 TSMC와의 3나노 전쟁에서 승기를 잡을 수 있다.

삼성전자가 계획대로 3나노 반도체 양산에 돌입하면 TSMC와의 격차를 줄이는 데도 상당한 도움이 될 것으로 보인다. 글로벌 시장조사업체 트렌드포스에 따르면 삼성전자의 시장 점유율은 지난해 4분기 18.3%에서 올해 1분기 16.3%로 2%포인트 하락했다. 반면 TSMC는 같은 기간 시장 점유율이 52.1%에서 53.6%로 상승했다. 지난해 4분기에 33.8%포인트 수준이던 두 회사의 점유율 격차는 올해 1분기 37.3%포인트로 더 벌어졌다.

업계 관계자는 "파운드리 한 우물만 40년 동안 판 TSMC에 비해 삼성은 파운드리 업력이 상대적으로 짧다. 파운드리 전문 인력도 부족한 상황에서 신공정 기반으로 먼저 3나노를 양산한다는 자체가 사실 말이 안 되는 건데 삼성전자는 이걸 하고 있다"고 말했다.

강경주 한경닷컴 기자 qurasoha@hankyung.com

관련뉴스