이 기사는 국내 최대 해외 투자정보 플랫폼 한경 글로벌마켓에 게재된 기사입니다.

작년 7월8일 아베 신조 전 일본 총리가 총탄에 사망한지 두 달여 뒤인 9월24일 대만 2대 도시 가오슝시에는 아베 동상이 세워졌다. 지역 유지들의 기부로 제작된 동상에는 "아베 전 총리는 생전 대만을 전력을 다해 지지했다. 감사의 마음을 담아 이 동상을 제작했다"라고 쓰여 있다.

지난 8일 아베 총리 사망 1주기를 맞아 식사 자리에서 만난 아베파 국회의원은 "아베 전 총리가 죽기 전에 가장 역점을 둔 활동이 일본-대만 경제협력이었다"라고 증언했다. 이를 위해 아베 전 총리의 최측근 의원들이 여러 차례 대만을 오갔다고 했다.

아베파는 일본의 집권여당 자민당내 최대 파벌이다. 아베파 주도로 자민당은 최근 수년에 걸쳐 반도체 관련 기업을 전폭적으로 지원했다. TSMC의 구마모토 공장 유치 역시 자민당 최대 파벌의 이러한 노력에 힘입은 성과라는 분석이다.하지만 TSMC 공장 유치에 대한 반응이 환영일색인 것만은 아니다.

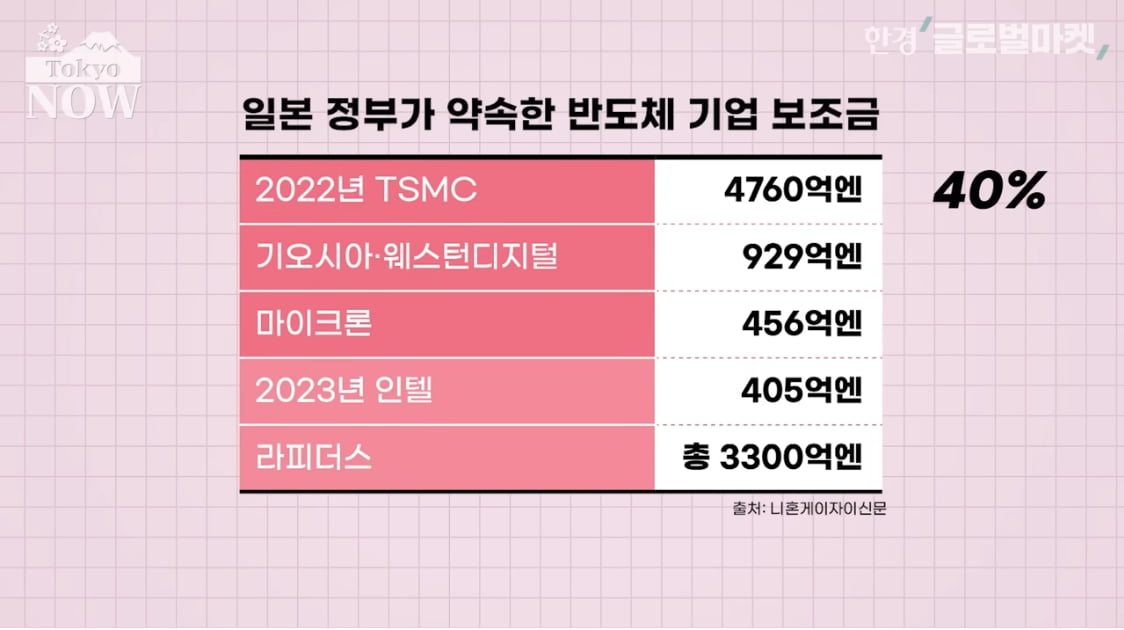

일본 정부는 구마모토 공장 건설비(1조2000억엔)의 40%인 4760억엔을 보조한다. 이 공장에서는 내년부터 12~28나노미터(1㎚=10억분의 1m)급 반도체를 생산한다. 주로 이미지 센서 등에 사용되는 반도체다. 최첨단 반도체(2nm 이하)에 비해서는 8~15년 이전의 기술이다. 일부에서 해외의 구형 반도체 공장을 유치하는데 왜 혈세를 5조원이나 쏟아붓느냐는 볼맨소리가 나오는 이유다.

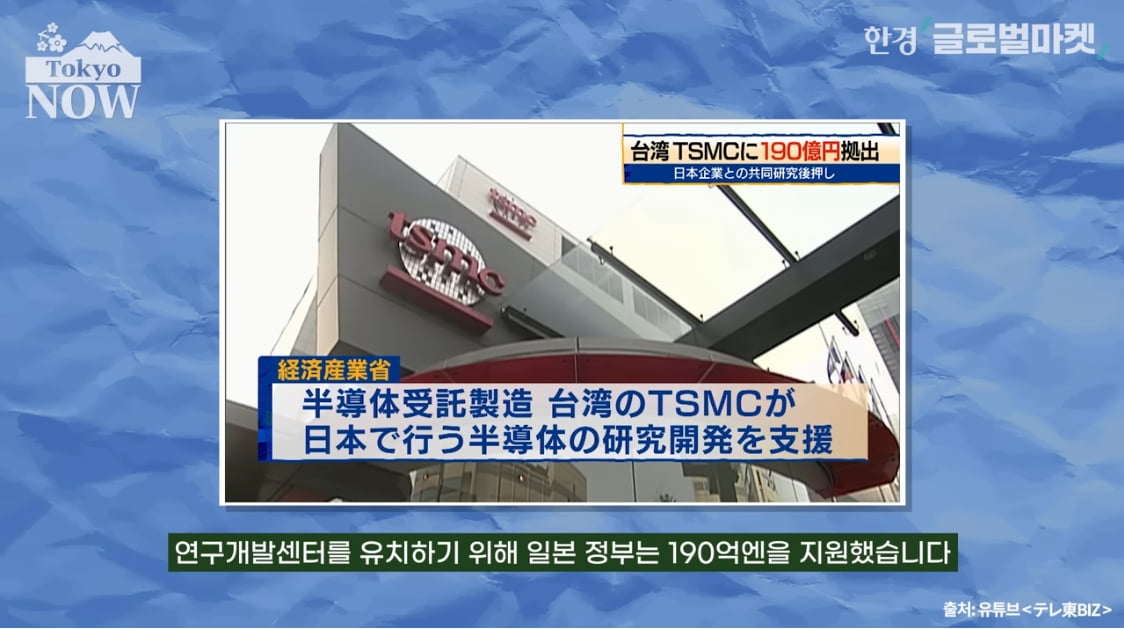

TSMC는 작년 6월24일 이바라키현 쓰쿠바시의 연구개발센터를 가동했다. 연구개발 센터를 유치하기 위해 일본 정부는 190억엔을 지원했다. 일본 정부는 "차세대 반도체 제조기술을 확립할 수 있게 됐다"라고 의미를 부여했다. 하지만 "조성사업의 성과(신기술)는 TSMC에 귀속된다"고 인정한다. TSMC가 이 연구소에서 얻는 성과와 지적재산권(IP)을 일본은 다룰 수 없다.

TSMC 구마모토 공장에도 비슷한 논리를 적용할 수 있다. 일본 정부는 TSMC의 공장을 유치함으로써 반도체의 안정적인 조달, 경제안보 확립, 산업부흥이 가능해졌다고 홍보한다. TSMC 구마모토 공장에서 생산되는 12~28nm 반도체는 바로 옆에 있는 소니그룹의 이미지 센서(CMOS) 공장에 주로 납품된다.

구마모토 공장에서 생산되는 반도체는 일본의 국내총생산(GDP)을 일부 늘리는 효과는 있겠지만 일본이 아니라 TSMC의 시장 점유율을 높여줄 뿐이다. 뿐만 아니라 소니의 이미지 센서는 대부분 애플과 중국 메이커의 스마트폰 카메라에 탑재된다. 애플과 샤오미의 스마트폰용 반도체를 생산하는게 일본의 경제안보와 무슨 관계가 있냐는 지적이다.

물론 TSMC를 일본에 유치하는 의미는 보이는 이상이라는 주장도 존재한다. 반도체 시장은 회로의 미세함에 따라 크게 최첨단 반도체(2나노미터 이하), 첨단 반도체(12~28나노미터), 범용 반도체(40나노미터 이상) 등 3가지로 나눌 수 있다. 일본의 기술은 범용 반도체 제조에 머물러 있다. TSMC를 유치함으로써 일본은 첨단 반도체도 생산하는 나라가 된다.

니혼게이자이신문의 간판 칼럼리스트 나카야마 아쓰시는 TSMC 공장 유치의 의미가 단순히 비어있는 첨단 반도체의 자리를 채우는데 그치지 않는다고 주장한다. 2nm 이하 최첨단 반도체 생산기술과도 직결되는 업적이라고 추켜세운다.

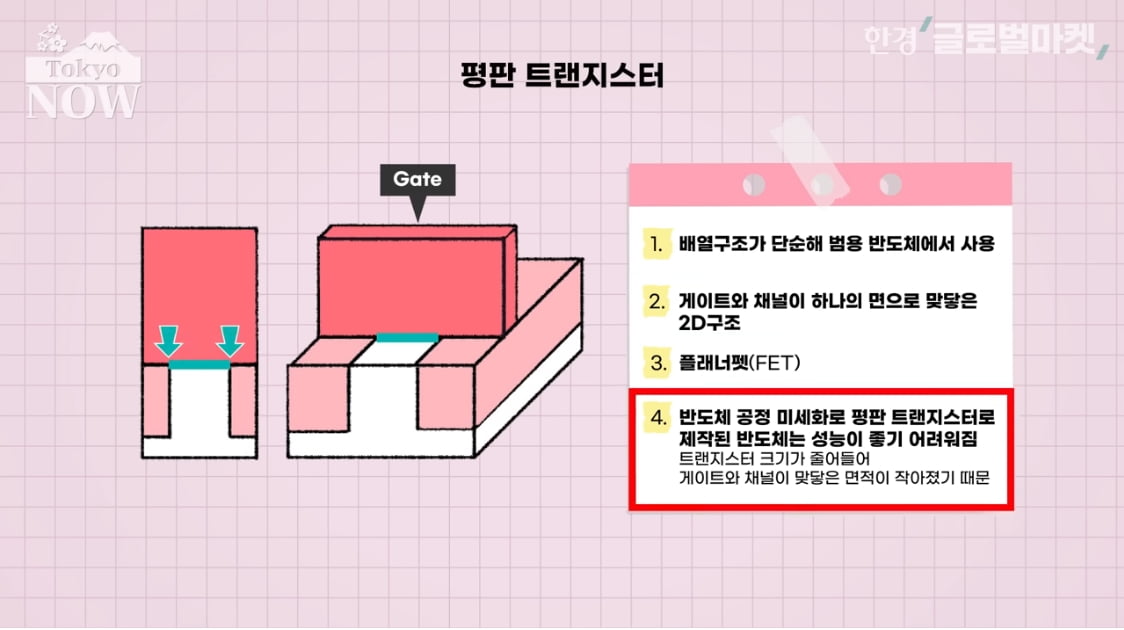

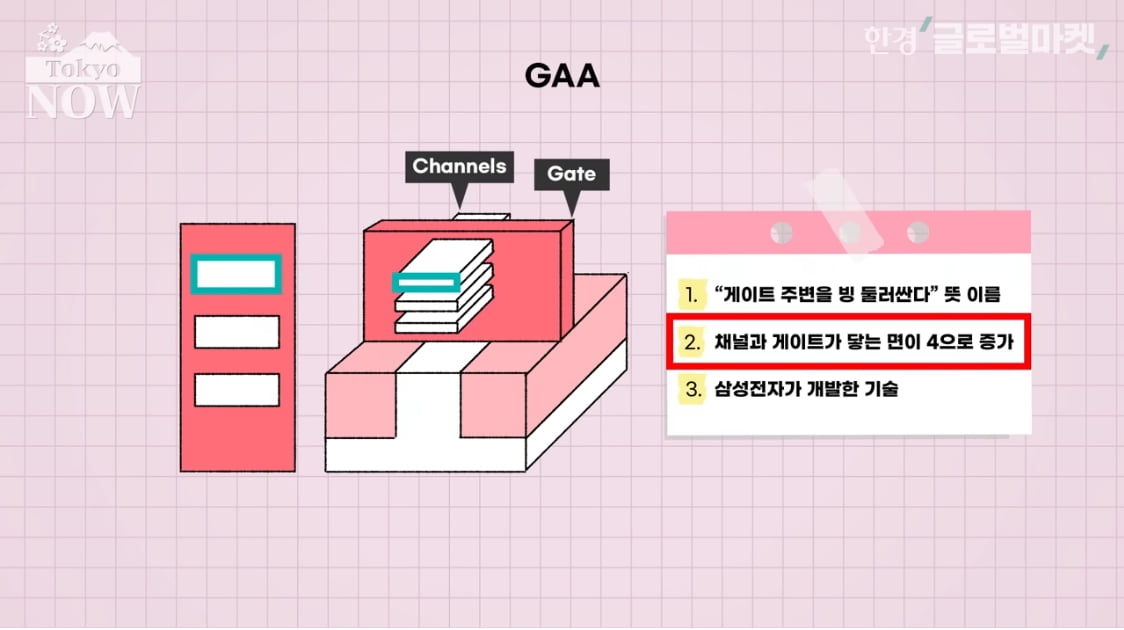

반도체 제조기술은 트랜지스트 배열구조에 따라 등급을 나눌 수 있다. 트랜지스터 배열구조는 반도체에서 전류를 흐르게 하는 '스위치' 역할을 한다. 트랜지스터에서 가장 중요한 부분이 '게이트'다. 게이트에 전압을 가하면 게이트와 맞닿아 있는 '채널'이 전기의 길을 열고 반대의 경우 전류를 차단한다.

게이트와 채널에서 새는 전류를 얼마나 줄이고 효율적으로 관리하느냐에 따라 반도체의 성능이 갈린다고 한다. 전력 효율성은 게이트와 채널이 닿는 면적이 클수록 높아진다.

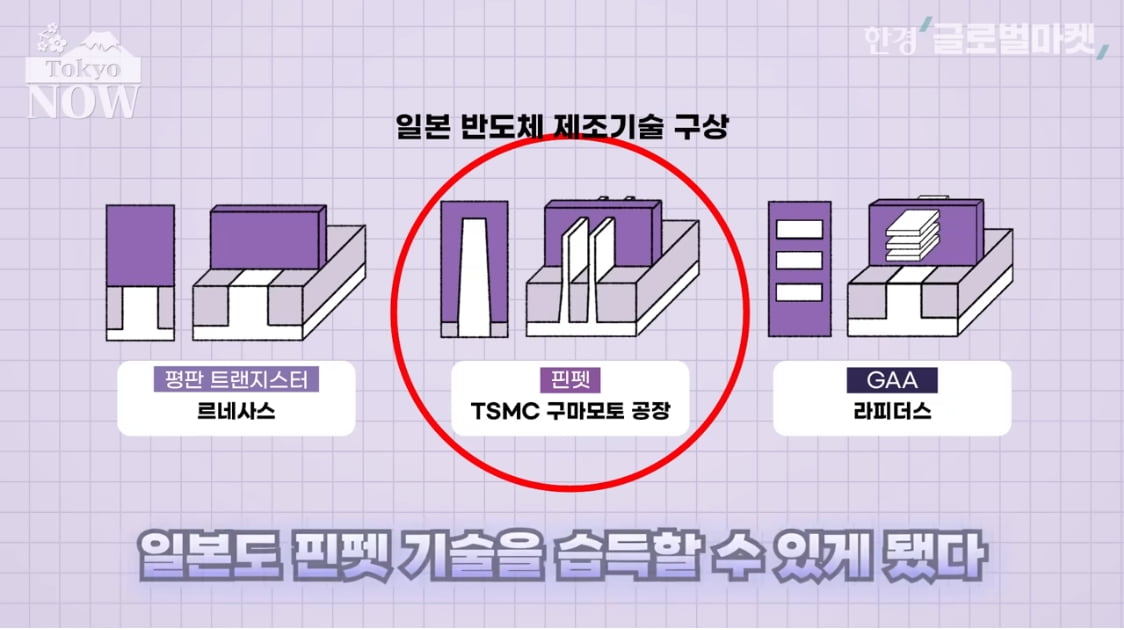

범용 반도체에는 배열구조가 가장 단순한 '평판 트랜지스터'가 사용된다. 게이트와 채널이 하나의 면으로 맞닿아 있는 '2D' 구조다. 플래너펫(FET)이라고도 한다. 반도체 공정이 미세화하면서 평판 트랜지스터로는 성능 좋은 반도체를 만들기 어렵게 됐다. 트랜지스터 크기가 줄어들면서 게이트와 채널이 맞닿는 면적이 작아졌기 때문이다.

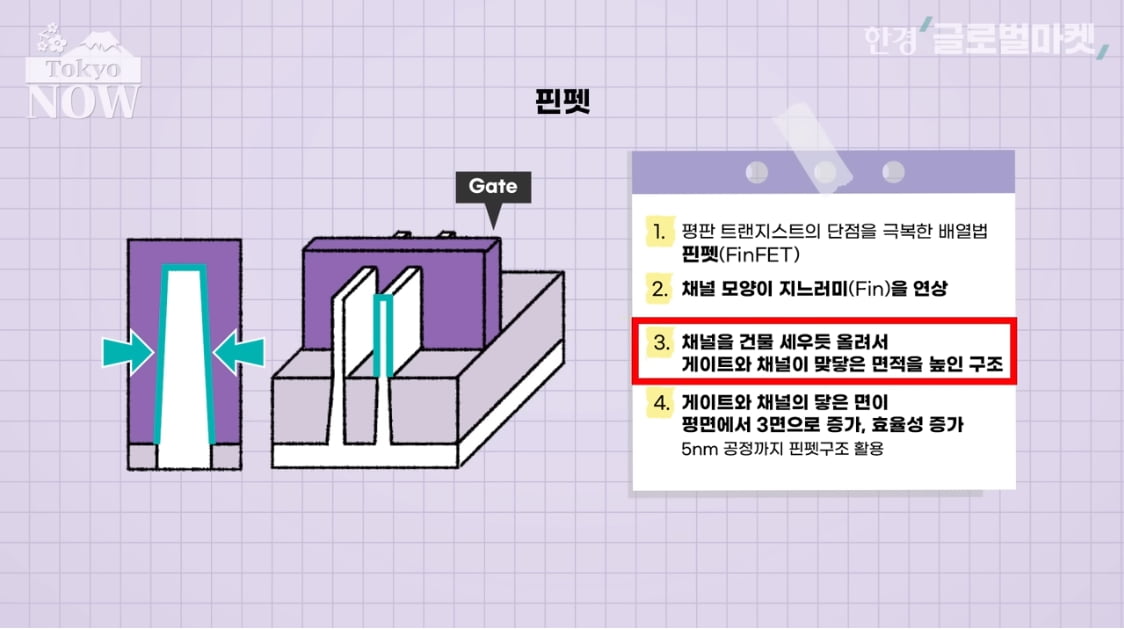

이를 극복한 배열법이 '핀펫(FinFET)'이다. 채널 모양이 지느러미(Fin)를 닮았다고 해서 붙은 이름이다. 채널을 건물을 세우듯 올려서 게이트와 채널이 맞닿는 면적을 높인 구조다. 게이트와 채널이 닿는 면이 '평면'에서 '3면'으로 늘면서 효율성도 크게 좋아졌다. 5nm 공정까지 핀펫구조가 활용된다. 최첨단 반도체 기술인 3nm 이후부터는 핀펫구조도 한계에 다다른다.

이를 넘어서기 위해 개발된 기술이 GAA(Gate All Around)다. '게이트 주변을 빙 둘러싼다'는 이름 그대로 채널과 게이트가 닿는 면이 3면에서 4면으로 늘어났다. GAA는 삼성전자가 개발한 기술이다.

2027년부터 2nm 반도체를 양산하겠다는 일본의 반도체 기술은 평판 트랜지스터에 머물러 있다. 핀펫 기술을 건너뛰고 GAA를 바로 습득하는 것은 현실적이지 않다. TSMC의 구마모토 공장은 핀펫 기술을 사용한다.

TSMC 공장을 유치함에 따라 일본도 핀펫 기술을 습득할 수 있게 됐다. 덕분에 IBM으로부터 GAA 기술을 습득하기 전 단계까지 기술력을 높일 수 있다는게 아츠시 칼럼리스트의 주장이다.

도쿄=정영효 특파원 hugh@hankyung.com

관련뉴스