"플랫폼 확장·원팀 정신으로 성공…DDR5 외 다른 D램에도 적용 예정"

(서울=연합뉴스) 강태우 기자 = 세계 최초로 10나노 6세대(1c) 기술 개발에 성공한 SK하이닉스[000660]가 해당 공정을 DDR5 D램은 물론 고대역폭 메모리(HBM)에도 확대 적용한다.

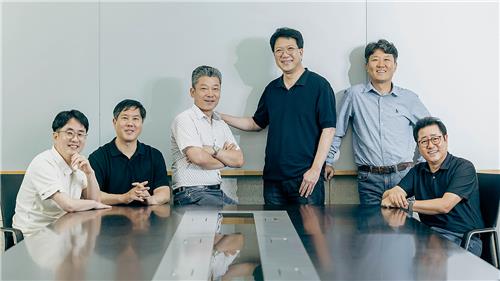

SK하이닉스는 10일 자사 뉴스룸을 통해 1c 기술 개발 과정과 혁신 기술 역량, D램 기술 로드맵에 대해 조명하는 임원들의 좌담회 내용을 공개했다.

SK하이닉스는 지난달 29일 10나노급 6세대(1c) 미세공정을 적용한 16Gb(기가비트) DDR5 D램을 개발하는 데 성공했다고 밝혔다. 이 제품은 고성능 데이터센터에 주로 활용될 예정으로, 내년부터 본격 공급된다.

반도체 업계는 10나노대 D램부터 세대별로 알파벳 기호를 붙여 호칭하고 있다. 1x(1세대), 1y(2세대), 1z(3세대), 1a(4세대), 1b(5세대)에 이어 1c는 6세대 기술이다.

세대를 거듭할수록 기술 난도가 크게 올라 수율 확보, 시간 단축 등에 어려움이 따른다.

이에 대해 정창교 D램 PE(프로덕트 엔지니어링) 담당 부사장은 1c 기술에서 주요 성능의 수준을 높이는 트리밍 기술을 활용해 수율과 품질을 확보했다고 설명했다. 트리밍 기술은 반도체 설계 변경 없이 전자식 퓨즈(eFuse)를 활용해 성능을 상향시키는 기술이다.

또 1b 플랫폼을 확장하는 방식으로 개발 시간과 시행착오도 줄였다.

1c 테크 태스크포스(TF)에 속한 오태경 부사장은 "1c 기술 개발을 총괄한 1c 테크 TF의 가장 큰 목표는 '1등 개발'이었다"며 "이를 위해 이미 우수성이 증명된 1b 플랫폼을 확장하는 방식으로 개발하는 전략을 선택했다"고 밝혔다.

이어 "기존의 3단계(테스트·설계·양산 준비) 개발 방식을 2단계(설계·양산 준비)로 효율화했으며, 커패시터 모듈과 같은 고난도의 기술 요소를 양산 공정에서 바로 개발하는 방식을 택했다"고 덧붙였다.

이를 통해 전 세대 제품 대비 2개월이나 시간을 단축했고, 공정 고도화 과정에서 발생할 수 있는 시행착오도 줄일 수 있었다고 한다.

10나노급 D램 기술의 미세공정 난이도가 극도로 높아지고 있는 상황에도 SK하이닉스가 해당 기술력 확보에 총력을 다하는 것은 인공지능(AI) 시대가 도래한 데 따른 것이다.

AI 반도체는 빠른 데이터 처리 속도뿐 아니라 데이터센터의 막대한 전력 소비에 대응할 전력 효율이 필요하다. D램 성능과 전력 효율을 향상시키는 방법 중 하나가 선폭 미세화다.

실제로 1c 기술을 적용한 DDR5의 동작 속도는 8Gbps(초당 기가비트)로 이전 세대인 1b DDR5보다 11% 빨라졌으며, 전력 효율은 9% 이상 개선됐다.

나아가 SK하이닉스는 극자외선(EUV) 공정에 신소재를 개발해 적용하고, 설계 기술 혁신을 통해 공정 효율을 극대화했으며 원가 절감까지 이뤄냈다.

정창교 부사장은 "1c 기술 개발 과정에서 가장 중요한 요소는 원팀 문화였다"며 "많은 기술적 도전을 극복하기 위해 각 조직이 긴밀하게 협력해 문제를 조기 발견했고, 해결했다"고 밝혔다.

손수용 개발테스트 담당 부사장은 "1c 개발 성공으로 SK하이닉스는 압도적인 기술 경쟁력을 입증했지만 1c DDR5는 시작일 뿐"이라며 "앞으로 1c 기술은 다양한 D램 제품에 적용돼 다양한 고객 니즈에 완벽하게 부응할 것"이라고 말했다.

SK하이닉스는 2026년 개발이 예상되는 7세대 HBM인 HBM4E부터 1c 기술을 적용한다는 계획이다.

1c 기술이 적용된 HBM4E는 SK하이닉스 최대 납품처인 엔비디아의 차세대 그래픽처리장치(GPU)에 탑재될 것으로 보인다.

burning@yna.co.kr

(끝)

<저작권자(c) 연합뉴스, 무단 전재-재배포, AI 학습 및 활용 금지>

관련뉴스